HyperTransport es una tecnología en desuso, pero su creación supuso un avance en la comunicación entre chips de un circuito integrado proporcionando un enlace avanzado de alta velocidad y rendimiento. No en vano, su nacimiento supuso la creación de una «autopista» de ultra alta velocidad y baja latencia, diseñada para la interconexión directa entre circuitos integrados. Su importancia radica en la eliminación de cuellos de botella en la transferencia de datos dentro de equipos críticos como routers, switches y servidores.

En este artículo te contamos un poco más sobre ella.

Índice de temas

Origen e historia de esta tecnología

HyperTransport es una tecnología de comunicaciones bidireccional que funciona tanto en serie como en paralelo ofreciendo un gran ancho de banda en conexiones punto a punto de baja latencia. Conocida también como Lightning Data Transport (LDT), se aplica en la comunicación entre chips de un circuito integrado ofreciendo un enlace (o bus) avanzado de alta velocidad y alto rendimiento. Se presenta como una conexión universal diseñada para reducir los cuellos de botella y el número de buses dentro de un sistema, suministrando un enlace de alto rendimiento a las aplicaciones incorporadas y facilitando sistemas de multiprocesamiento altamente escalables.

Fue inventada por AMD con contribuciones de otros socios y es administrada y licenciada por el HyperTransport Consortium, empresa ubicada en Texas que se encarga de llevar a cabo su desarrollo y promoción.

La primera versión se creó en 2001. Desde entonces fue evolucionando para ofrecer velocidades más altas y mayores funcionalidades, pero manteniendo su baja latencia. Fue en 2006, con la versión 3.0 cuando se empezó a utilizar para sustituir el sistema Front Side Bus (FSB).

Así las cosas, fue empleada por varios fabricantes como AMD en procesadores x86y chipsets; PMC-Sierra, Broadcom y Traza Microelectronics en microprocesadores; MIPS, NVIDIA, VIA Technologies y Silicon Integrated Systems en chipsets; HP, Sun Microsystems, IBM y Flextronics en servidores; Cray, Newisys, QLogic y XtremeData en sistemas informáticos de alto rendimiento; y Cisco en routers.

HyperTransport vs. Front Side Bus (FSB)

HyperTransport se desarrolló con el objetivo de eliminar el sistema digital Front Side Bus (FSB), el antiguo canal de comunicación principal en ordenadores. El también denominado bus frontal transfiere datos entre los componentes de una computadora -conecta el procesador con la memoria principal-, y se solía emplear en algunos de los microprocesadores antiguos de Intel para comunicarse con el chipset. Incluía señales de datos, direcciones y control, además de señales de reloj que sincronizan su funcionamiento.

Fue con la versión 3.0 de HyperTransport cuando varios fabricantes de chips abandonaron FSB y optaron por la nueva tecnología. También se implementó para interconexiones entre microprocesadores MIPS, servidores, servidores informáticos de alto rendimiento y en routers y switches. Intel, por su parte, lo reemplazó por otras tecnologías como QPI (Quick Path Interconnect) o UPI (Ultra Path Interconnect).

¿Cómo funciona la arquitectura de HyperTransport? Características principales

HyperTransport está basada en paquetes. Cada uno de ellos consiste en un conjunto de palabras de 32 bits independientemente del ancho físico de la conexión. La primera palabra de un paquete es siempre una palabra de comando. Si un paquete contiene una dirección, los últimos 8 bits de la palabra de comando estarán enlazados con la siguiente palabra de 32 bits para formar una dirección de 40 bits. Además, se permite anteponer otra palabra de control de 32 bits cuando se necesite una dirección de 64 bits. Las restantes palabras de 32 bits en un paquete formarán la información útil. Las transferencias, independientemente de su longitud actual, estarán formadas siempre por múltiplos de 32 bits.

Estos paquetes entran en segmentos conocidos como tiempos bit. El número de tiempos bit necesarios depende del ancho de la interconexión. Esta tecnología puede usarse para generar mensajes de gestión de sistemas, señales de interrupciones, expedir sondas a dispositivos adyacentes o procesadores y E/S en general y hacer transacciones de datos.

Normalmente se pueden usar dos tipos diferentes de comandos de escritura: avisados y no-avisados. Las escrituras avisadas no precisan una respuesta del destino. Son usadas primordialmente para dispositivos con un gran ancho de banda como tráfico a Uniform Memory Access o transferencias de Acceso directo a memoria. Las escrituras no-avisadas precisan una respuesta del tipo «destino hecho». La lectura también puede provocar que el receptor genere una respuesta.

Velocidad de interconexión

Soporta conexiones auto-negociadas para determinar la velocidad. Su velocidad de transferencia máxima, utilizando líneas de 32 bits, tiene por cada uno de sus 2 buses un total de 20.8 GB/s (2.6 GHz * (32 bits / 8), lo que supone la suma de 41.6 GB/s en ambas direcciones.

Se pueden mezclar también enlaces de varios anchos en una sola aplicación (por ejemplo, 2×8 en vez de 1×16). Esto permite una velocidad de interconexión mayor entre la memoria principal y la CPU y una menor entre los periféricos que lo precisen.

Utiliza tecnología DDR (Double Data Rate), transmitiendo datos en el flanco ascendente y descendente, con frecuencias que alcanzan hasta 3.2 GHz (o más,), logrando tasas de transferencia de hasta 51.2 GB/s.

Latencia, bidireccionalidad y conexión punto a punto

Esta tecnología tiene mucha menos latencia que otras soluciones anteriores, además se caracteriza por su bidireccionalidad permitiendo la transferencia de datos simultánea en ambas direcciones, lo que aumenta la eficiencia en la comunicación entre procesadores y memoria.

A ello se suma la conexión punto a punto que ofrece al conectar dos componentes directamente, eliminando la necesidad de buses compartidos lentos y optimizando la escalabilidad en sistemas multiprocesador.

¿Cuáles fueron las versiones de HyperTransport?

Existen diferentes versiones de HyperTransport. La 1.0 fue lanzada en 2001. Posteriormente la siguieron la 1.1 en 2002; la 2.0 en 2004; la 3.0 en 2006 y la 3.1 en 2008. Con un ancho máximo de enlace de 32 Bit, sus diferentes evoluciones han ido aumentado su funcionamiento desde los 800 MHz hasta 3.2 GHz. También soporta tecnología DDR, lo cual la posibilita para alcanzar un máximo de 5200 MT/s (2600 MHz hacia cada dirección: entrada y salida) funcionando a su máxima velocidad (2.6 GHz).

¿Cuál es la situación actual de HyperTransport en 2026?

Aunque fue popular en PCs, hoy todavía está presente en aplicaciones integradas, networking y comunicaciones. Sin embargo, se considera una tecnología legacy y se ha ido reemplazando por otras. De hecho, su uso actual es limitado, centrándose en sistemas embebidos antiguos o equipos de redes muy específicos que aún requieren esa arquitectura.

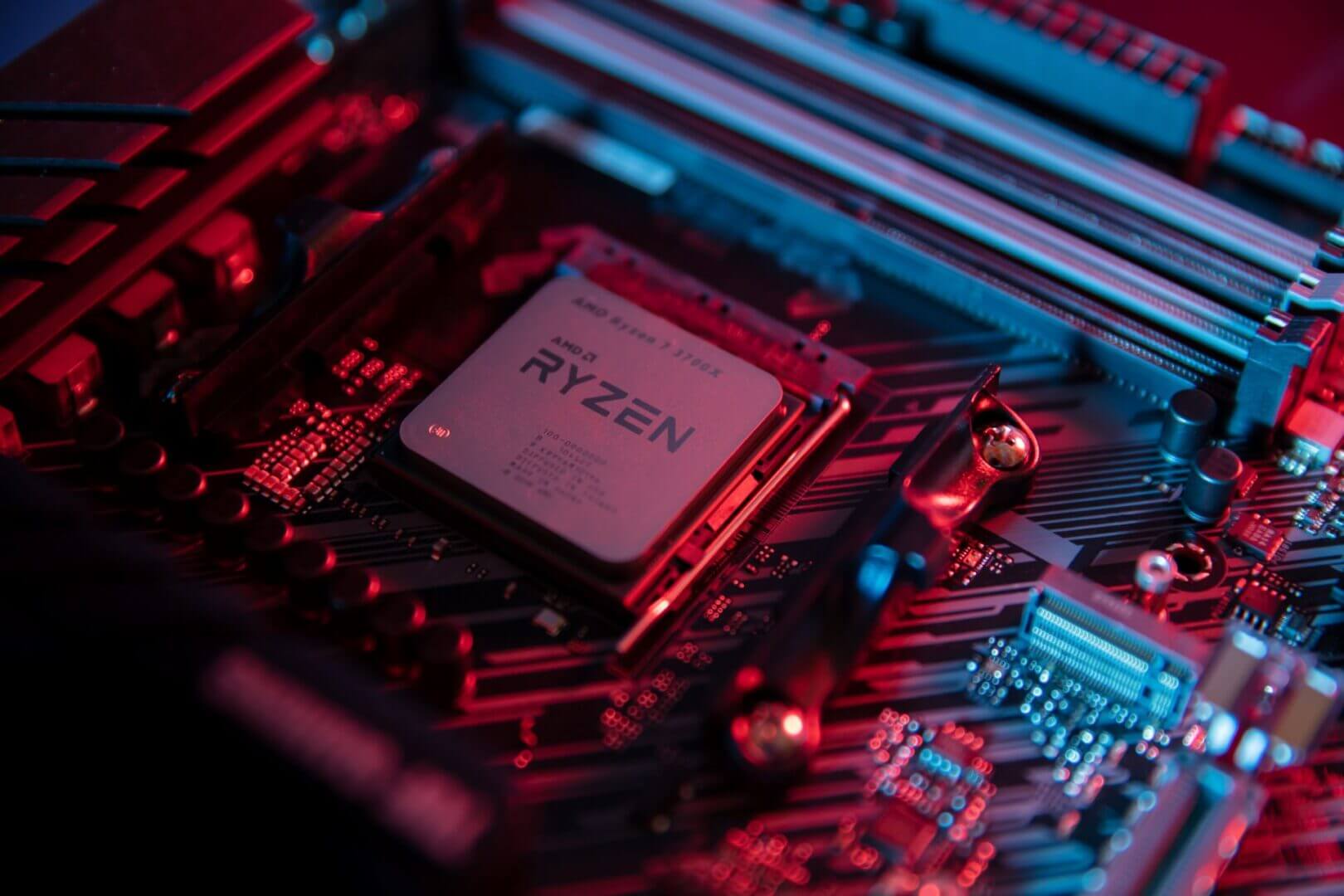

De Hypertransport a AMD Infinity Fabric

En los últimos años, AMD ha ido desarrollando diferentes tecnologías para ir potenciar el rendimiento del procesador y del equipo de cómputo. Entre estas innovaciones se encuentra Infinity Fabric, una propuesta para comunicar elementos de los nuevos procesadores.

Esta plataforma de comunicación e interconexión de sistemas fue patentada por el propio fabricante que la presentó en 2017 con la implementación de los nuevos procesadores Ryzen y su arquitectura Zen.

Con ella se busca comunicar los componentes internos de un procesador a nivel de datos y de control para lo que se utilizan dos niveles o planos de comunicación: SDF o Scalable Data Fabric y SCF o Scalable Control Fabric. El término Scalable hace referencia a que es un bus que en principio se puede extender de forma eficiente a una cantidad de nodos cada vez más grande de forma sencilla.

SDF es el sistema de comunicación evolución de HyperTransport por el que viajan los datos de Infinity Fabric. Este se encarga de transportar los datos desde cada núcleo hacia la memoria caché o el I/O Hub (interfaz de entrada/salida de la CPU). De igual forma, se encarga de interconectar los carriles de memoria RAM, PCIe e incluso USB a la CPU solamente con las restricciones que se marquen en el diseño propio del procesador. Por ello no usa una topología totalmente definida, sino que a veces funciona en bus (caché – núcleo) o en malla (enlaces PCIe).

Aplicaciones históricas de Hypertransport

Como hemos comentado al inicio de este artículo, Hypertransport se utilizó como bus de interconexión principal en gran parte de la familia de procesadores AMD (x86-64) como los Athlon 64 en 2003, facilitando la comunicación entre el controlador de memoria integrado y el resto de la placa.

Asimismo, habilitó sistemas multiproceso altamente escalables al permitir la conexión directa entre procesadores y fue utilizado para conectar el procesador con el chipset de la placa base, mejorando la velocidad de comunicación en comparación con los buses tradicionales.

Otra de las aplicaciones antiguas que todavía permanecen en sistemas heredados se circunscriben al entorno de networking y comunicaciones para aumentar el flujo de datos de algunos equipos de redes. Además de su incursión como estándar abierto en sistemas embebidos, de almacenamiento y comunicaciones para conectar componentes de alta velocidad.

Preguntas frecuentes sobre hypertransport

¿AMD sigue usando HyperTransport en sus procesadores modernos?

No, AMD no utiliza HyperTransport en sus procesadores modernos de consumo (como las series Ryzen 7000, 8000 o 9000, basadas en la arquitectura Zen 4 y Zen 5). Aunque fue fundamental para el proveedor desde 2001 para conectar el procesador con el chipset y la memoria, ha sido sustituido por tecnologías más rápidas.

¿Qué velocidad máxima alcanza la tecnología HyperTransport?

Alcanza velocidades máximas de transferencia de datos de hasta 6400 MT/s (megatransferencias por segundo) en su versión 3.1, operando a una frecuencia de reloj de 3.2 GHz.